Something went wrong. Please refresh the page and try again.

Something went wrong. Please refresh the page and try again.

Notifications can be turned off anytime from settings.

Item(s) Added To cart

Qty.

Something went wrong. Please refresh the page and try again.

Something went wrong. Please refresh the page and try again.

Exchange offer not applicable. New product price is lower than exchange product price

Please check the updated No Cost EMI details on the payment page

Exchange offer is not applicable with this product

Exchange Offer cannot be clubbed with Bajaj Finserv for this product

Product price & seller has been updated as per Bajaj Finserv EMI option

Please apply exchange offer again

Your item has been added to Shortlist.

View AllYour Item has been added to Shopping List

View AllSorry! VLSI System Design Online Course by twenty19 is sold out.

You will be notified when this product will be in stock

| Chapter 1 | |

| 1. | Introduction |

| Chapter 2 | |

| 1. | Basics of MOS Transistor: Introduction to MOSFET |

| 2. | Basics of MOS Transistor: Gate Voltage & Accumulation of Negative Charge |

| 3. | Basics of MOS Transistor: NChannel Formation Between Source & Drain |

| 4. | Basics of MOS Transistor: Impact Of Substrate Potential On threshold Voltage |

| 5. | Basics of MOS Transistor: Threshold voltage with body complete |

| 6. | Basics of MOS Transistor: Exercise 1 |

| 7. | Basics of MOS Transistor: Excercise 2 |

| Chapter 3 | |

| 1. | SpecificationsToCHIP |

| 2. | Chip Dimension And Intro To Preplaced Cells |

| 3. | Pre Placed Cells Concluded |

| 4. | Decoupling Capacitors And Power Plan |

| 5. | Example For Netlist And Pin Placement |

| 6. | Pin Placement And Intro To PNR |

| 7. | Example Continued For PNR |

| 8. | Placement And Optimize Placement |

| 9. | Optimize Placement Continued |

| 10. | Optimize Placement Concluded |

| 11. | STA ideal clocks |

| 12. | STA ideal clocks with Setup Time. |

| 13. | STA ideal clocks with Example |

| 14. | STA ideal multiple clocks |

| 15. | STA ideal multiple clocks with example |

| 16. | STA Data slew check |

| 17. | STA Data slew check example |

| 18. | ClockTreeSyntehsis HTree |

| Chapter 4 | |

| 1. | Introduction to Clock Tree |

| 2. | Skew Pulse Width Quality Checks |

| 3. | Duty Cycle Latency Quality Checks |

| 4. | Latenct Power Quality Check |

| 5. | Power Quality Check |

| 6. | Power Crosstalk Quality Check |

| 7. | Delta Delay Quality Check |

| 8. | Glitch Quality Check |

| Chapter 5 | |

| 1. | HTree Skew Check |

| 2. | HTree Pulse Width Duty Cycle Check |

| 3. | Htree Latency Power Check |

| Chapter 6 | |

| 1. | Clock tree Modelling |

| 2. | Clock Tree Buffering |

| 3. | Clock Tree Building |

| 4. | Clock Tree Observations |

| Chapter 7 | |

| 1. | HTree Buffering Observations |

| 2. | HTree Skew Check |

| 3. | HTree Pulse Width Check Regular And Clock Buffer |

| 4. | Inverter Resistance Difference |

| 5. | Inverter Resistance Match Solution |

| 6. | HTree CBUF Pulse Width Check MET |

| 7. | Duty Cycle Latency Power check Intro |

| 8. | Dynamic Short Circuit Power Revisited |

| 9. | Leakage Power Revisit |

| Chapter 8 | |

| 1. | Optimization CheckList |

| 2. | Short Circuit current Revisited |

| 3. | Leakage Current Revisited |

| 4. | Clock Tree Optimized |

| 5. | Optimized Clock Tree Power Latency Check |

| Chapter 9 | |

| 1. | Clock Tree Uneven Clk End Points Spread |

| 2. | Logical To Physical Connection |

| 3. | Uneven clock Endpoints HTree CheckList |

| 4. | Advanced HTree Million Flops |

| Chapter 10 | |

| 1. | Power Aware CTS Intro To Gates |

| 2. | Delay Table Usage 1 |

| 3. | Delay Table Usage 2 |

| 4. | Clock Gating Using AND Gate and Skew Cal |

| 5. | Skew Issue Solution |

| 6. | OR AND simultaneous clock gating technique |

| 7. | NAND gates as clock gating cells |

| 8. | Clock Gating Technique on Real Chip |

| Chapter 11 | |

| 1. | Setup timing Analysis Real Clocks |

| 2. | Intro To Data Arrival And Required Time |

| 3. | Setup Timing Degrade by unbalanced Skew |

| 4. | Hold Timing Analysis Real Clocks |

| 5. | Hold Timing Degrade by unbalanced Skew |

| 6. | Summary |

| 11.1 | Mega QUIZ |

Project Based Learning

This course will cover end-to-end description from basic Device Physics to Chip Design as we know Clock Tree Networks are Pillars and Columns of a Chip. You will learn about concepts of Industrial VLSI circuits, Clock Tree Synthesis Quality Checks, H-Tree and much more.You will also get to do a project in which you need to solve a Circuit and analyse the results. And finally suggest the better circuit solution for improved Chip performance

Get Certified

On successful completion of the course, you will get an E-Certificate from Twenty19.

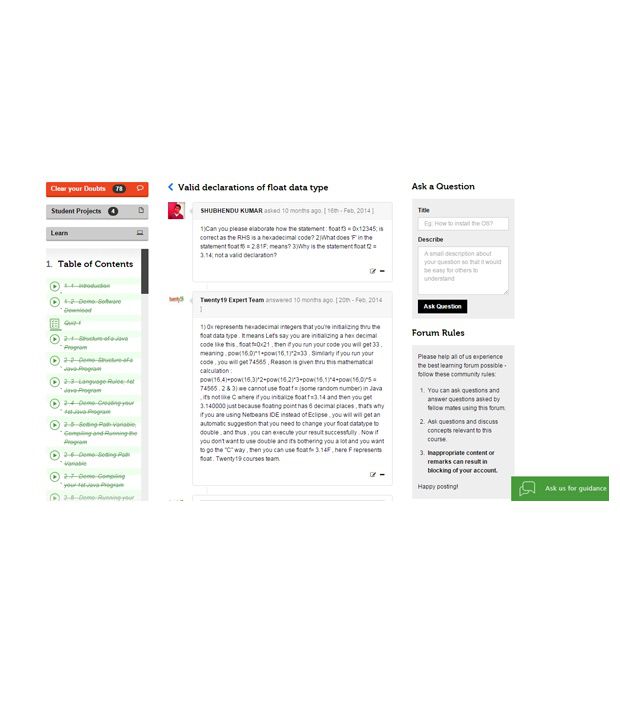

Clarify your Doubts

You can ask all the questions in 'Clarify your Doubts' forum anytime;

course experts will answer all your questions.

Learn Everything, Anywhere, Anytime

India's Largest Online Education Marketplace

The images represent actual product though color of the image and product may slightly differ.

Register now to get updates on promotions and

coupons. Or Download App